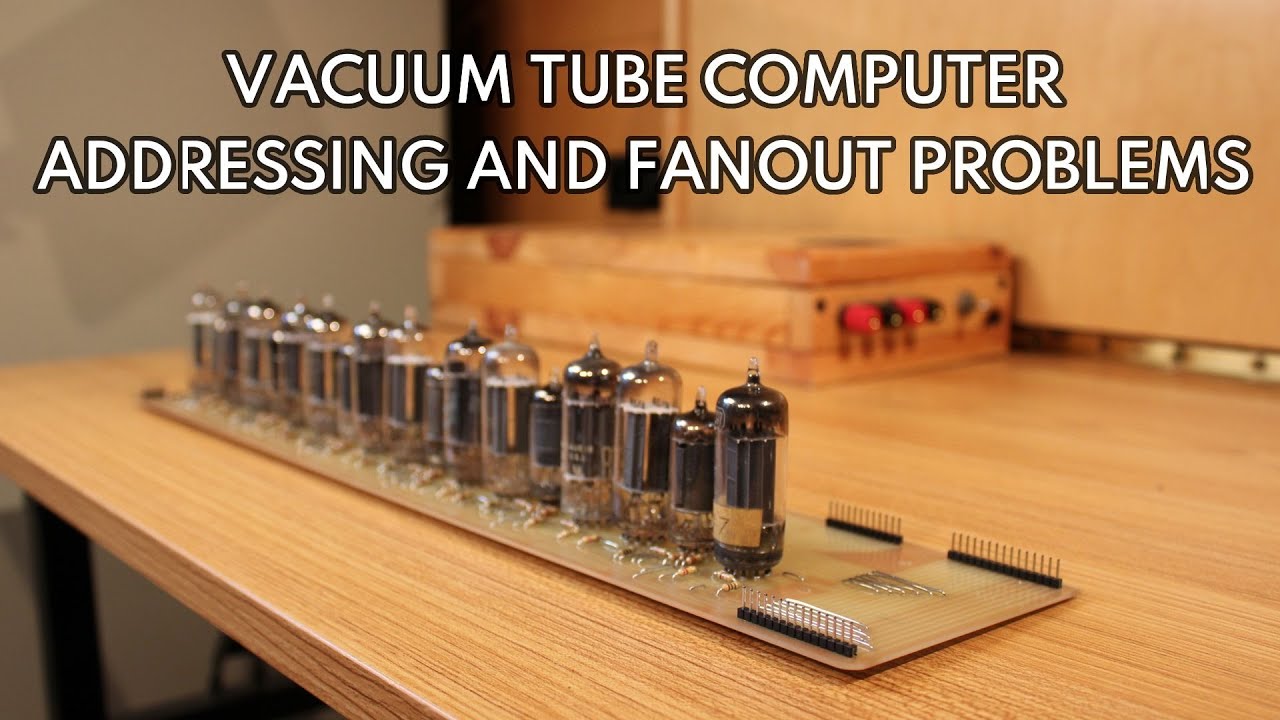

In order to select the desired cell in the computer’s memory array, the six address lines from the processor and their logical negations must be connected to the inputs of the memory decoder array, which requires driving 16 NOR gate inputs per address line (normal and inverted). This runs squarely into the design problem of fan-out, where the abstraction of logic design must confront the gritty reality of electrical engineering. Driving a gate input high or low requires the output of the gate driving it to source a certain amount of current, and trying to drive too many inputs will pull down the voltage on the signals driving them, resulting in unreliable operation or total failure. With modern integrated circuit logic families, this is rarely a problem: outputs on 74HC series CMOS logic can drive fifty or more inputs of the same family unless operating speed requires limiting capacitance of the interconnections. Vacuum tube logic, especially if operating at low voltage, has far more limited fan-out and for an application like this the signals driving the decoder array must be buffered by drivers able to provide the current required to drive 16 inputs. So, another circuit board chock full of tubes joins the party.